XV-FA90BK/XV-FA92SL XV-FA95GD

# JVC SERVICE MANUAL

DVD AUDIO/VIDEO PLAYER

# XV-FA90BK / XV-FA92SL XV-FA95GD

AUDIO VIDEO VIDEO UD

### Each difference point

| Model     | Body color |  |

|-----------|------------|--|

| XV-FA90BK | Black      |  |

| XV-FA92SL | Silver     |  |

| XV-FA95GD | Gold       |  |

# < ATTENTION ! >

Please pull out the AC plug code after the standby indicator lights pushing the power supply button without fail after completing the repair.

The mechanism becomes initialed position.

There is a possibility to break when carrying in not initialed position the mechanism but the state.

# Contents

| Safety precautions 1-2            | Disassembly method 1-6                  |

|-----------------------------------|-----------------------------------------|

| Preventing static electricity 1-3 | Adjustment method 1-24                  |

| Importance admistering            | Troubleshooting 1-28                    |

| point on the safety 1-4           | Description of major ICs 1-32           |

| Precautions for service 1-5       | Glossary of term and abbreviations 1-53 |

# -Safety Precautions-

- 1. This design of this product contains special hardware and many circuits and components specially for safety purposes. For continued protection, no changes should be made to the original design unless authorized in writing by the manufacturer. Replacement parts must be identical to those used in the original circuits. Services should be performed by qualified personnel only.

- 2. Alterations of the design or circuitry of the product should not be made. Any design alterations of the product should not be made. Any design alterations or additions will void the manufacturer's warranty and will further relieve the manufacture of responsibility for personal injury or property damage resulting therefrom.

- 3. Many electrical and mechanical parts in the products have special safety-related characteristics. These characteristics are often not evident from visual inspection nor can the protection afforded by them necessarily be obtained by using replacement components rated for higher voltage, wattage, etc. Replacement parts which have these special safety characteristics are identified in the Parts List of Service Manual. Electrical components having such features are identified by shading on the schematics and by (A) on the Parts List in the Service Manual. The use of a substitute replacement which does not have the same safety characteristics as the recommended replacement parts shown in the Parts List of Service Manual may create shock, fire, or other hazards.

- 4. The leads in the products are routed and dressed with ties, clamps, tubings, barriers and the like to be separated from live parts, high temperature parts, moving parts and/or sharp edges for the prevention of electric shock and fire hazard. When service is required, the original lead routing and dress should be observed, and it should be confirmed that they have been returned to normal, after re-assembling.

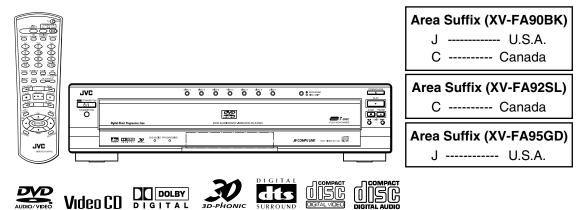

- 5. Leakage current check (Electrical shock hazard testing)

After re-assembling the product, always perform an isolation check on the exposed metal parts of the product (antenna terminals, knobs, metal cabinet, screw heads, headphone jack, control shafts, etc.) to be sure the product is safe to operate without danger of electrical shock.

Do not use a line isolation transformer during this check.

Plug the AC line cord directly into the AC outlet. Using a "Leakage Current Tester", measure the leakage current from each exposed metal parts of the cabinet, particularly any exposed metal part having a return path to the chassis, to a known good earth ground. Any leakage current must not exceed 0.5mA AC (r.m.s.).

#### Alternate check method

Plug the AC line cord directly into the AC outlet. Use an AC voltmeter having, 1,000 ohms per volt or more sensitivity in the following manner. Connect a 1,500  $\Omega$  10W resistor paralleled by a 0.15 $\mu$ F AC-type capacitor

between an exposed metal part and a known good earth ground. Measure the AC voltage across the resistor with the AC voltmeter.

Move the resistor connection to each exposed metal part, particularly any exposed metal part having a return path to the chassis, and measure the AC voltage across the resistor. Now, reverse the plug in the AC outlet and repeat each measurement. Voltage measured any must not exceed 0.75 V AC (r.m.s.). This corresponds to 0.5 mA AC (r.m.s.).

# Warning

- 1. This equipment has been designed and manufactured to meet international safety standards.

- 2. It is the legal responsibility of the repairer to ensure that these safety standards are maintained.

- 3. Repairs must be made in accordance with the relevant safety standards.

- 4. It is essential that safety critical components are replaced by approved parts.

- 5. If mains voltage selector is provided, check setting for local voltage.

Burrs formed during molding may be left over on some parts of the chassis. Therefore, pay attention to such burrs in the case of preforming repair of this system.

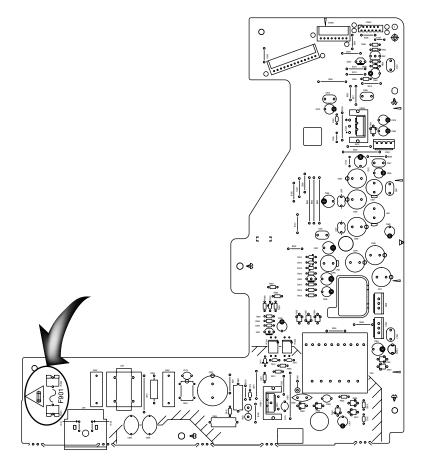

In regard with component parts appearing on the silk-screen printed side (parts side) of the PWB diagrams, the parts that are printed over with black such as the resistor (--), diode (+-) and ICP (-) or identified by the " $\underline{\wedge}$ " mark nearby are critical for safety.

When replacing them, be sure to use the parts of the same type and rating as specified by the manufacturer. (Except the J and C version)

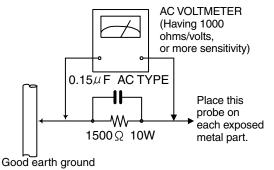

# **Preventing static electricity**

Electrostatic discharge (ESD), which occurs when static electricity stored in the body, fabric, etc. is discharged, can destroy the laser diode in the traverse unit (optical pickup). Take care to prevent this when performing repairs.

# 1.1. Grounding to prevent damage by static electricity

Static electricity in the work area can destroy the optical pickup (laser diode) in devices such as DVD players. Be careful to use proper grounding in the area where repairs are being performed.

#### 1.1.1. Ground the workbench

1. Ground the workbench by laying conductive material (such as a conductive sheet) or an iron plate over it before placing the traverse unit (optical pickup) on it.

#### 1.1.2. Ground yourself

1. Use an anti-static wrist strap to release any static electricity built up in your body.

#### 1.1.3. Handling the optical pickup

- 1. In order to maintain quality during transport and before installation, both sides of the laser diode on the replacement optical pickup are shorted. After replacement, return the shorted parts to their original condition. (Refer to the text.)

- 2. Do not use a tester to check the condition of the laser diode in the optical pickup. The tester's internal power source can easily destroy the laser diode.

# 1.2. Handling the traverse unit (optical pickup)

- 1. Do not subject the traverse unit (optical pickup) to strong shocks, as it is a sensitive, complex unit.

- 2. Cut off the shorted part of the flexible cable using nippers, etc. after replacing the optical pickup. For specific details, refer to the replacement procedure in the text. Remove the anti-static pin when replacing the traverse unit. Be careful not to take too long a time when attaching it to the connector.

- 3. Handle the flexible cable carefully as it may break when subjected to strong force.

- 4. It is not possible to adjust the semi-fixed resistor that adjusts the laser power. Do not turn it

# Importance Admistering point on the Safety

#### Full Fuse Replacement Marking

Graphic symbol mark (This symbol means fast blow type fuse.)

should be read as follows ;

#### **FUSE CAUTION**

FOR CONTINUED PROTECTION AGAINST RISK OF FIRE, REPLACE ONLY WITH SAME TYPE AND RATING OF FUSES ;

# F901:1.6 A / 125 V

#### Marquage Pour Le Remplacement Complet De Fusible

Le symbole graphique (Ce symbole signifie fusible de type á fusion rapide.)

doit être interprété comme suit ;

PRECAUTIONS SUR LES FUSIBLES

POUR UNE PROTECTION CONTINUE CONTRE DES RISQUES D'INCENDIE, REMPLACER SEULEMENT PAR UN FUSIBLE DU MEME TYPE ;

F901:1.6 A / 125 V

# **Precautions for Service**

Handling of Traverse Unit and Laser Pickup

- 1. Do not touch any peripheral element of the pickup or the actuator.

- 2. The traverse unit and the pickup are precision devices and therefore must not be subjected to strong shock.

- 3. Do not use a tester to examine the laser diode. (The diode can easily be destroyed by the internal power supply of the tester.)

- 4. To replace the traverse unit, pull out the metal short pin for protection from charging.

- 5. When replacing the pickup, after mounting a new pickup, remove the solder on the short land which is provided at the center of the flexible wire to open the circuit.

- 6. Half-fixed resistors for laser power adjustment are adjusted in pairs at shipment to match the characteristics of the optical block.

Do not change the setting of these half-fixed resistors for laser power adjustment.

#### Destruction of Traverse Unit and Laser Pickup by Static Electricity

Laser diodes are easily destroyed by static electricity charged on clothing or the human body. Before repairing peripheral elements of the traverse unit or pickup, be sure to take the following electrostatic protection:

- 1. Wear an antistatic wrist wrap.

- 2. With a conductive sheet or a steel plate on the workbench on which the traverse unit or the pick up is to be repaired, ground the sheet or the plate.

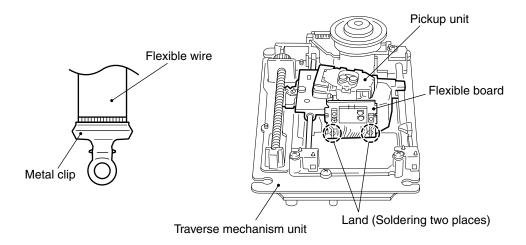

- 3. After removing the flexible wire from the connector (CN101), short-circuit the flexible wire by the metal clip.

- 4. Short-circuit the laser diode by soldering the land which is provided at the two places of the flexible board for the pickup. After completing the repair, remove at the two places of the solder to open the circuit.

# **Disassembly method**

# <Main body>

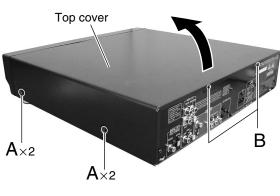

# ■ Removing the top cover (See Fig.1)

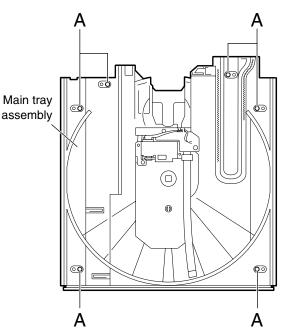

- 1. Remove the four screws  ${\bf A}\,$  on each side of the body.

- 2. Remove the two screws  ${\bf B}\,$  on the back of the body.

- 3. Lift the rear part of the top cover and remove in the direction of the arrow while pulling both sides of the top cover outward.

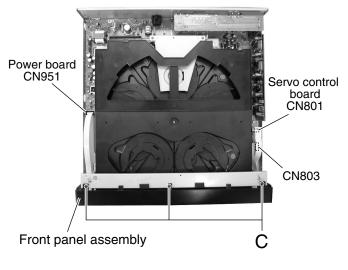

# Removing the front panel assembly (See Fig.2 and 3)

- Prior to performing the following procedure, remove the top cover.

- 1. Disconnect the card wire from connector CN801 and CN803 on the servo control board, and CN951 on the power board respectively.

- 2. Remove the three screws **C** on the upper side of the body.

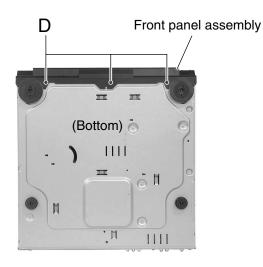

- 3. Remove the three screws **D** on the bottom of the body.

Remove the front panel assembly toward the front.

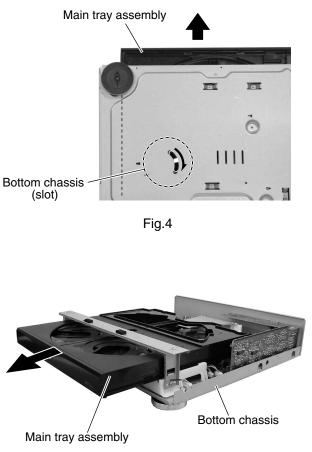

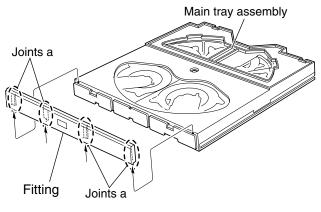

# ■Removing the main tray assembly (See Fig.4 to 7)

- Prior to performing the following procedure, remove the top cover and the front panel assembly.

- 1. Turn over the body and insert a screwdriver into the slot of the bottom chassis, then move it in the direction of the arrow in Fig.4. The main tray assembly will move forward.

- 2. Draw the main tray assembly toward the front manually.

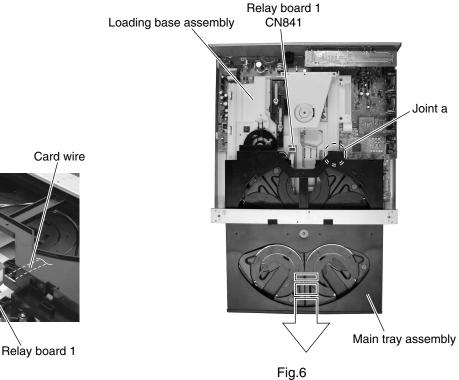

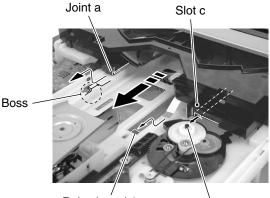

- 3. Bring up the joint **a** over the boss of the loading base assembly, and remove the main tray assembly toward the front.

- 4. Disconnect the card wire, on the back of the main tray assembly, from connector CN841 on the relay board 1.

Fig.5

Joint a Loading base assembly Boss

Fig.7

# -Reattaching the main tray assembly-(See Fig.8 to 10)

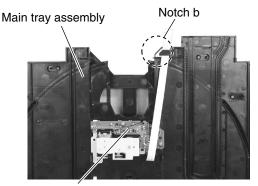

- 1. Turn over the main tray assembly and pass the card wire extending from the photo sensor board through the notch **b**, in advance (Fig.8).

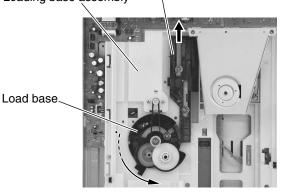

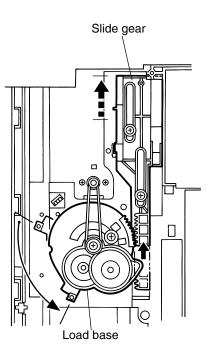

- 2. From above the loading base assembly, turn the load base counterclockwise until the slide gear stops at the back end (Bring down the traverse mechanism assembly).

- 3. Reattach the main tray assembly to the loading base assembly while fitting to the groove on the right and left sides of the loading base assembly.

- 4. Connect the card wire through the notch **b** to connector CN841 on the relay board 1.

- Reattach the main tray assembly while fitting the slot c to the shaft.

Photo sensor board Fig.8

Loading base assembly Slide gear

Fig.9

Relay board 1 Shaft CN841 Fig.10

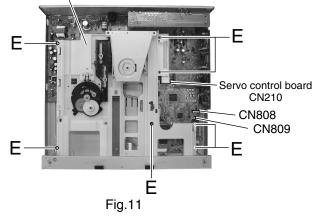

■Removing the loading base assembly (See Fig.11)

- Prior to performing the following procedure, remove the top cover, the front panel assembly and the main tray assembly.

- 1. Disconnect the wire from connector CN808, CN809 and the card wire from CN210 on the servo control board respectively.

- 2. Remove the seven screws **E** attaching the loading base assembly.

Loading base assembly

### Removing the rear panel (See Fig.12)

- · Prior to performing the following procedure, remove the top cover.

- 1. Remove the fourteen screws F attaching the rear panel.

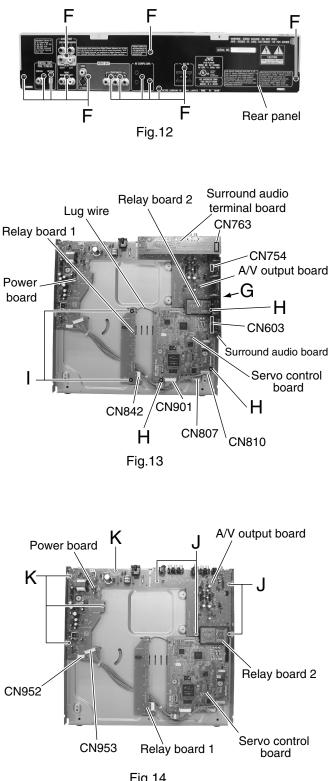

# Removing each board (See Fig.13,14)

· Prior to performing the following procedure, remove the top cover, the front panel assembly, the main tray assembly, rear panel and the loading base assembly.

#### -Surround audio board -

- 1. Pull out the surround audio terminal board from connector CN763.

- 2. Remove the screw G attaching the surround audio board.

- 3. Pull out the surround audio board from connector CN754 and CN603.

#### -Servo control board-

- 1. Pull out the relay board 2 on the upper side of the body.

- 2. Disconnect the wire from connector CN807, CN810 and CN901 on the servo control board respectively.

- 3. Remove the screw I attaching the lug wire.

- 4. Remove the three screws H attaching the servo control board.

#### -Relay board 1-

- 1. Disconnect the wire from connector CN842 on the relay board 1.

- 2. Remove the two screws I attaching the relay board.

### -A/V output board-

- 1. Pull out the relay board 2 on the upper side of the body.

- 2. Remove the four screws J attaching the A/V output board.

#### -Power board -

- 1. Disconnect the wire from connector CN952 and CN953 on the power board.

- 2. Remove the four screws K on the upper side of the body.

Fig.14

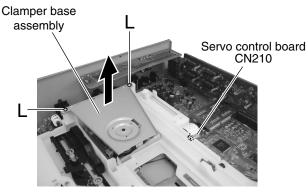

# ■Removing the traverse mechanism assembly (See Fig.15 and 16)

• Prior to performing the following procedure, remove the top cover and the front panel assembly.

REFERENCE: There is no need to remove the loading base assembly.

- 1. Eject the main tray assembly toward the front referring to "Removing the main tray assembly".

- 2. Remove the two screws L and pull out the clamper base assembly upward.

- 3. Disconnect the card wire from connector CN210 on the servo control board.

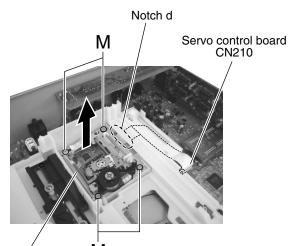

- 4. Remove the four screws **M** and the traverse mechanism assembly upward.

CAUTION: When reattaching the traverse mechanism assembly, pass the card wire extending from the traverse mechanism assembly through the notch **d** of the elevator base.

# <Front panel assembly>

• Prior to performing the following procedure, remove the top cover and the front panel assembly.

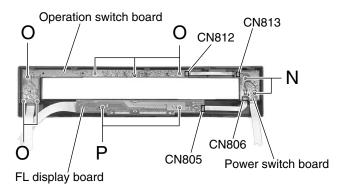

# Removing the power switch board (See Fig.17)

- 1. Remove the two screws  ${\bf N}\,$  on the back of the front panel assembly.

- 2. Disconnect the card wire from connector CN813 and CN806 on the power switch board.

### Removing the operation switch board (See Fig.17)

- 1. Remove the six screws **O** on the back of the front panel assembly.

- 2. Disconnect the card wire from connector CN812 on the operation switch board.

# ■ Removing the FL display board (See Fig.17)

- 1. Remove the two screws **P** on the back of the front panel assembly.

- 2. Disconnect the card wire from connector CN805 on the FL display board.

Fig.15

Traverse mechanism M assembly Fig.16

Fig.17

# XV-FA90BK/XV-FA92SL/XV-FA95GD

# <Loading base assembly unit>

• Prior to performing the following procedures, remove the top cover, the front panel assembly, the main tray assembly, the loading base assembly.

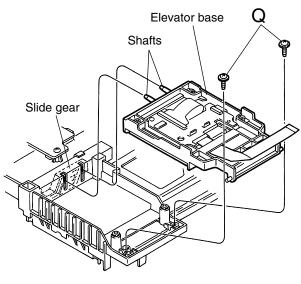

# Removing the elevator base (See Fig.18 and 19)

- REFERENCE: It is not necessary to remove the traverse mechanism assembly from the elevator base. As the removing procedure of the traverse mechanism, please refer to "Removing the traverse mechanism assembly".

- 1. Turn over the loading base assembly and remove the two screws **Q**.

- 2. Remove the elevator base upward.

Fig.18

Fig.19

#### - Reattaching the elevator base -

REFERENCE: From above the loading base, turn the load base counterclockwise until the slide gear stops at the back end as shown in Fig.19.

- 1. Reattach the elevator base to the loading base assembly while fitting the two shafts on the side of the elevator base to the grooves of the slide gear.

- 2. Reattach the two screws  ${\bf Q}.$

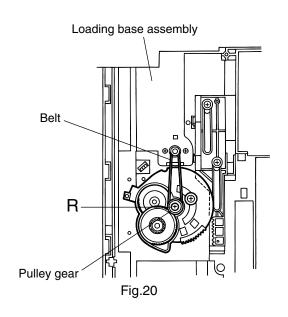

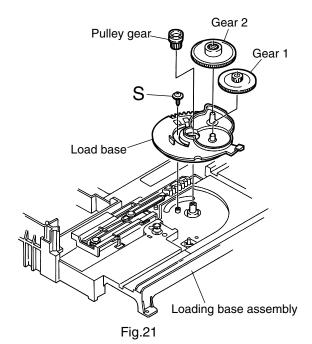

# Removing the belt / load base / slide gear

- Prior to performing the following procedures, remove the elevator base.

- 1. Remove the belt on the upper side of the loading base assembly.

- 2. Remove the screw  ${\bf R}\,$  attaching the pulley gear.

- 3. Remove the pulley gear, the gear 1, the gear 2 and the belt respectively.

- 4. Remove the screw  ${\boldsymbol{\mathsf{S}}}$  and the load base upward.

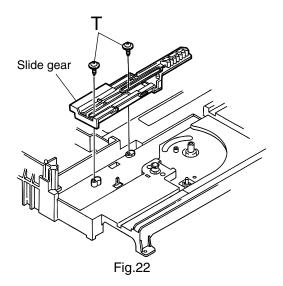

- 5. Remove the two screws **T** and the slide gear upward.

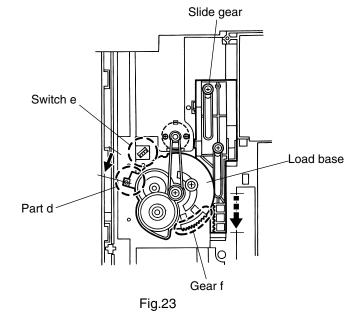

# CAUTION: When reattaching the slide gear and the load base,

- 1. Move the slide gear toward the front until it stops (Fig.23).

- Make sure that the part d of the load base is out of alignment with the switch e and that the gear f is disengaged from the slide gear.

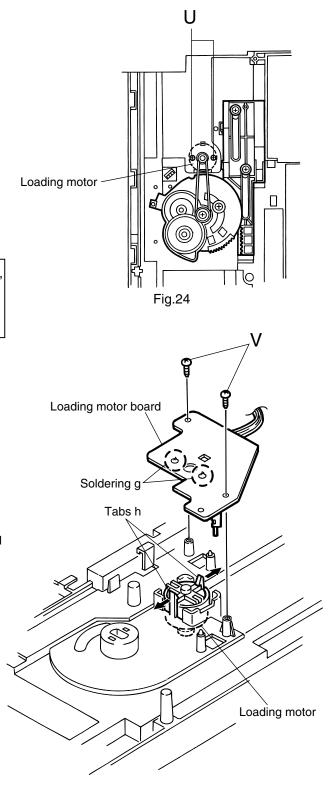

# Removing the loading motor / loading motor board (See Fig.24 and 25)

- 1. Remove the two screws **U** attaching the loading motor on the upper side of the loading base assembly.

- 2. Turn over the loading base assembly and unsolder the two soldering **g** on the loading motor board.

- 3. Remove the two screws **V** attaching the loading motor board.

- 4. Spread apart the two tabs **h** and pull out the loading motor.

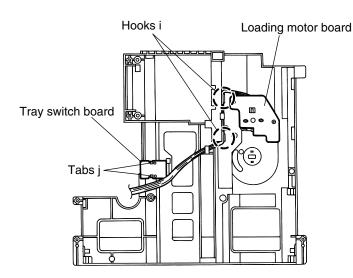

CAUTION: When reattaching the loading motor board, settle the wires on the two hooks **i** on the loading base assembly and draw the other end to the left as shown in Fig.26.

# Removing the tray switch board (See Fig.26)

1. Turn over the loading base assembly, and remove the tray switch board while spreading apart the two tabs **j**.

Fig.26

# <Traverse mechanism unit>

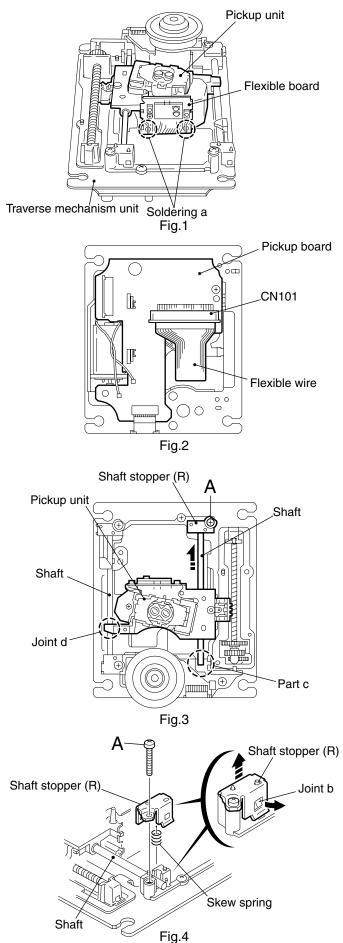

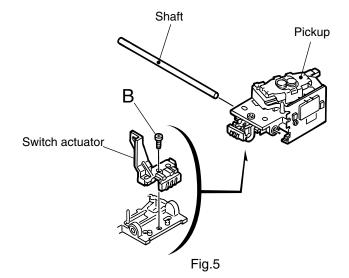

# ■Removing the pickup (See Fig.1 to 5)

- % It is not necessary to remove the traverse mechanism unit.

- 1. Solder soldering **a** on the flexible board next to the pickup unit.

- 2. From the bottom of the traverse mechanism unit, disconnect the flexible wire from CN101 on the pickup board.

ATTENTION: Disconnecting the flexible wire without soldering may cause damage to the pickup.

- Remove the screw A attaching the shaft stopper (R) on the upper side of the traverse mechanism unit. Pull the side of the shaft stopper (R) outward to release the joint b and remove it upward. Remove the skew spring at the same time.

- 4. Move the shaft in the direction of the arrow to release it from the part **c**.

- 5. Release the joint **d** with the shaft and remove the pickup with the shaft.

- 6. Pull out the shaft.

- 7. Remove the screw **B** attaching the switch actuator.

#### XV-FA90BK/XV-FA92SL/XV-FA95GD

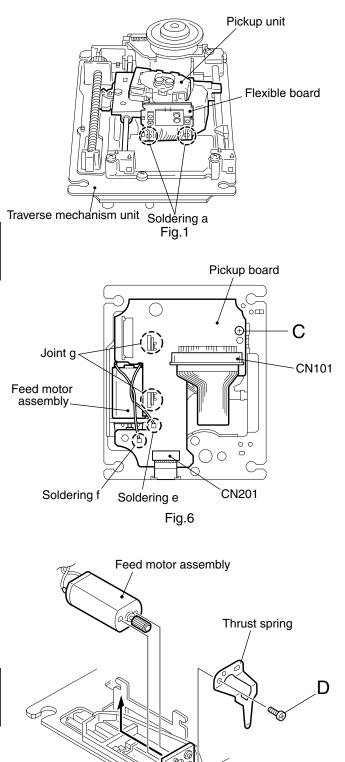

#### Removing the pickup board (See Fig.1 and 6)

- % It is not necessary to remove the traverse mechanism unit.

- 1. Solder soldering **a** on the flexible board next to the pickup unit.

- 2. From the bottom of the traverse mechanism unit, disconnect the flexible wire from CN101 on the pickup board.

ATTENTION: Disconnecting the flexible wire without soldering may cause damage to the pickup.

- Disconnect the card wire from connector CN201 on the pickup board and unsolder the soldering e and f on the harnesses

- 4. Remove the screw **C** attaching the pickup board and release the two joints **g**.

#### ■ Removing the feed motor assembly (See Fig.1, 6 and 7)

- Prior to performing the following procedure, remove the traverse mechanism unit.

- 1. Solder soldering **a** on the flexible board next to the pickup unit.

- 2. From the bottom of the traverse mechanism unit, disconnect the flexible wire from CN101 on the pickup board.

ATTENTION: Disconnecting the flexible wire without soldering may cause damage to the pickup.

- 3. Remove the pickup board.

- 4. Remove the two screws **D** attaching the feed motor assembly and remove the thrust spring. Move the feed motor assembly in the direction of the arrow to pull it out from the feed holder.

Feed holder assembly

Fig.7

D

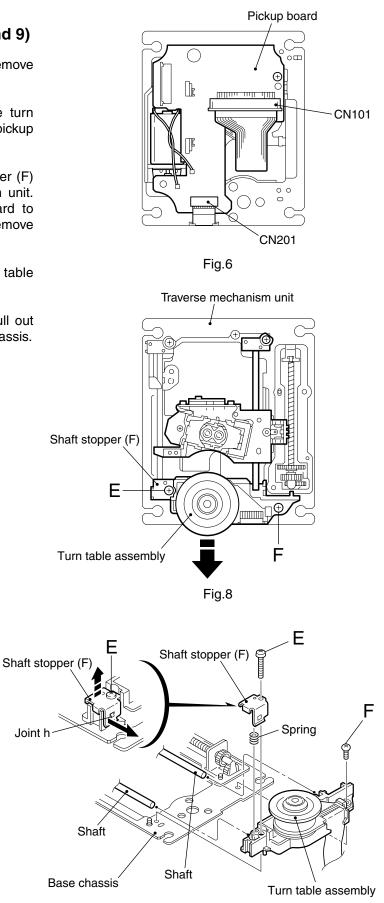

# ■Removing the turn table assembly (See Fig.6, 8 and 9)

- Prior to performing the following procedure, remove the traverse mechanism unit.

- 1. Disconnect the card wire extending from the turn table assembly, from connector CN201 on the pickup board.

- Remove the screw E attaching the shaft stopper (F) on the upper side of the traverse mechanism unit.

Pull the side of the shaft stopper (F) outward to release the joint h and remove it upward. Remove the spring at the same time.

- 3. Remove the screw **F** attaching the turn table assembly.

- 4. Move the turn table assembly outward and pull out from the shaft. Then remove it from the base chassis.

Fig.9

# <Main tray assembly unit>

• Prior to performing the following procedures, remove the top cover, the front panel assembly and the main tray assembly.

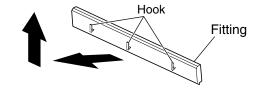

# ■ Removing the fitting (See Fig.1)

1. Remove the fitting on the front side of the main tray assembly while releasing the four joints **a** upward.

\* Lifts for above while pulling the hook in three places to front side.

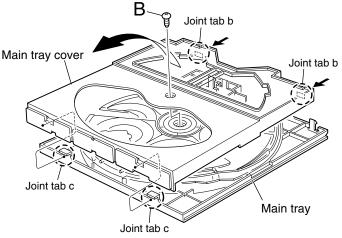

#### Removing the main tray cover and the main tray (See Fig.2 and 3)

- Prior to performing the following procedure, remove the fitting.

- 1. Remove the six screws **A** attaching the main tray on the under side of the main tray assembly.

- 2. Remove the screw **B** attaching the main tray cover on the upper side of the main tray assembly.

- 3. Push the two joint tabs **b** on the back of the main tray assembly to release the main tray cover from the tray bottom. Disengage the joint tabs **c** of the main tray from the main tray cover.

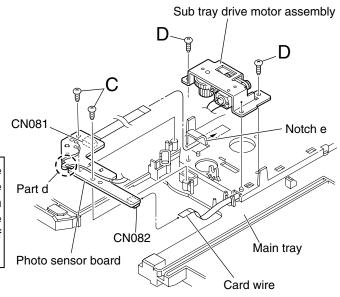

#### Removing the photo sensor board and the sub tray drive motor assembly (See Fig.4)

- 1. Turn over the main tray assembly and remove the two screws **C** attaching the photo sensor board.

- 2. Disconnect the card wire from connector CN082 on the photo sensor board.

REFERENCE: Make sure to disconnect the card wire from the photo sensor board. If the photo sensor board is pulled out from the main tray without disconnecting the card wire, the cam switch side inside of the main tray may be damaged.

3. Remove the two screws **D** attaching the sub tray drive motor assembly.

Fig.4

#### -When reassembling,-

• Attach the two wires to the part **d** on the photo sensor board, and before reattaching the photo sensor board, connect the card wire to connector CN082 and pass the card wire extending from connector CN081 through the notch **e** of the main tray.

#### XV-FA90BK/XV-FA92SL/XV-FA95GD

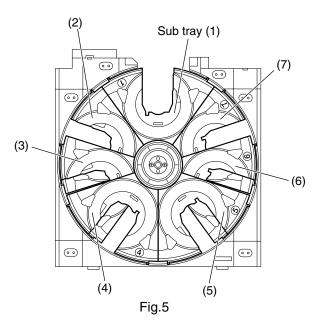

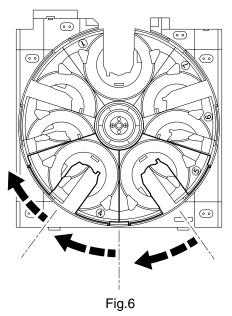

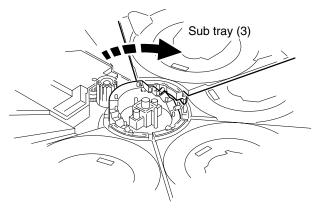

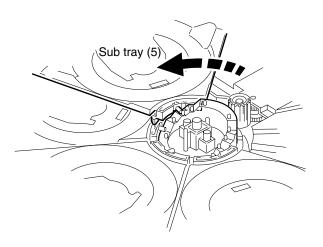

### ■Sub tray position and operation check (See Fig.5 and 6)

• Prior to performing the following procedures, remove the fitting and the main tray cover.

CAUTION: Make sure the sub trays are set as shown in Fig.5. When moving the sub trays, put the sub trays which come to the position (4) and (5) forward in turn.

> Prior to moving the sub trays by hand, the sub tray drive motor assembly must be removed in advance referring to the preceding page.

> Do not put the sub trays forward except at the position (4) and (5).

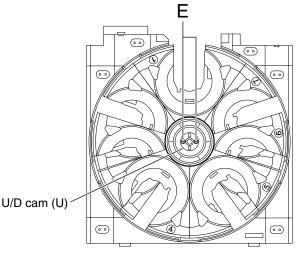

# ■ Removing the U/D cam (U) (See Fig.7)

- Prior to performing the following procedure, remove the main tray cover.

- 1. Remove the two screws **E** attaching the U/D cam (U) on the upper side of the main tray assembly.

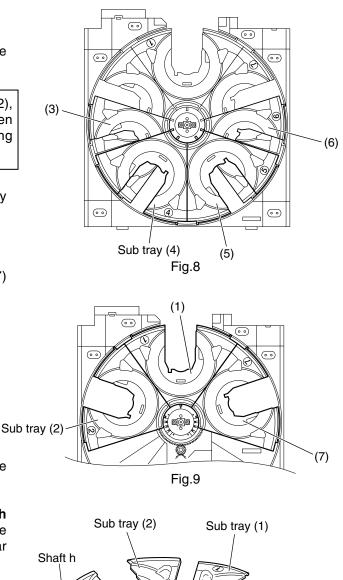

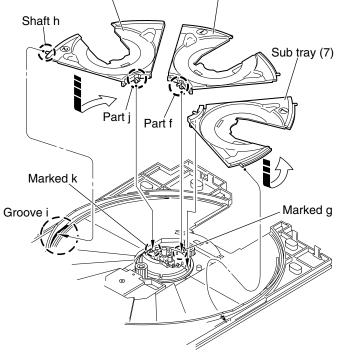

# ■ Removing the sub trays (See Fig.8 to 14)

• Prior to performing the following procedure, remove the main tray cover and the U/D cam (U).

CAUTION: Remove the sub tray assembly (4), (3), (2), (5), (6), (7) and (1) in order. When reattaching, observe the following procedure without fail.

- 1. Remove the sub tray (4) and (3) from the main tray upward.

- 2. Remove the sub tray (2) upward.

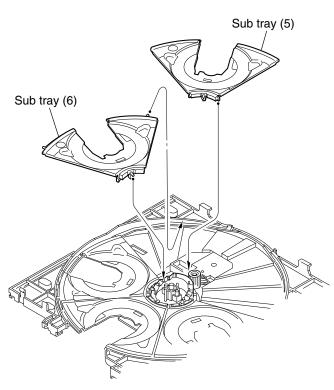

- 3. Similarly, remove the sub tray (5) , (6) and (7) upward.

- 4. At last, remove the sub tray (1) upward.

# -Reattaching the sub tray -

- 1. Reattach the sub tray (1) while fitting the part **f** to the groove of the ACT. gear (1) marked **g**.

- 2. Reattach the sub tray (2) while inserting the shaft **h** into the groove **i** of the main tray, and at the same time, fitting the part **j** to the groove of the ACT. gear (1) marked **k**.

Move the sub tray (2) toward the tray (1).

3. Similarly, reattach the sub tray (7).

# XV-FA90BK/XV-FA92SL/XV-FA95GD

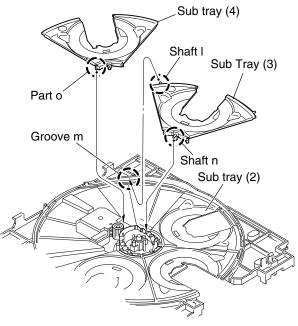

4. Reattach the sub tray (3) while inserting the shaft **I** into the groove **m** of the main tray, and at the same time, putting the shaft **n** on the U/D cam (L). Then, move the sub tray (3) toward the sub tray (2) until it stops.

REFERENCE: At this point, the sub tray (3) is on top of the sub tray (2).

5 Reattach the sub tray (4) while fitting the part **o** to the ACT.gear (2) on the main tray.

CAUTION: Make sure the part **o** of the sub tray (4) engages with the ACT. gear (2) correctly in the center of the main tray.

REFERENCE: At this point, the sub tray (4) is on top of the sub tray (3).

6. Reattach the sub tray (6) and (5) in the same way.

CAUTION: Make sure that the trays are attached to the correct position and that they can be moved. To move the sub trays manually, the sub tray drive motor assembly must be removed in advance.

Fig.13

Fig.14

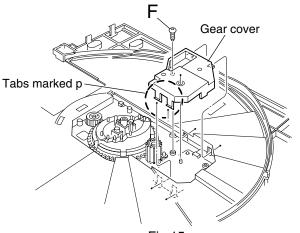

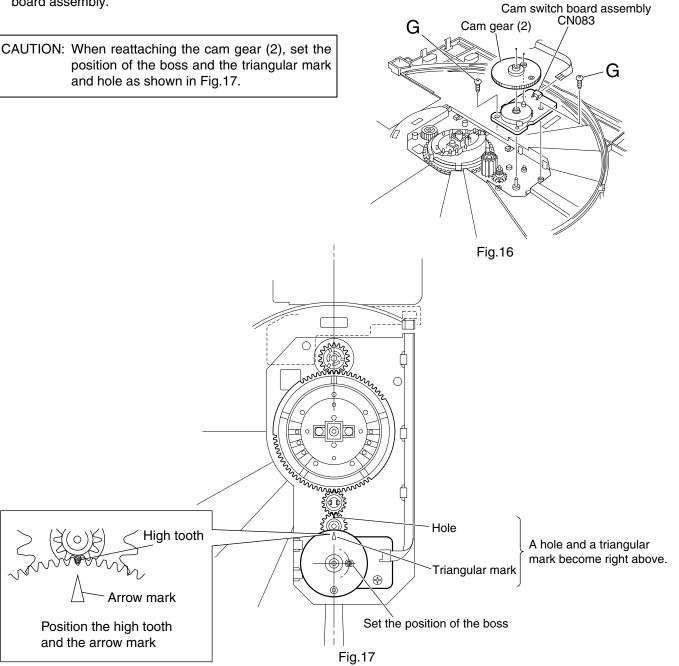

# Removing the cam switch board assembly (See Fig.15 to 17)

- · Prior to performing the following procedure, remove the main tray cover, the U/D cam (U) and the sub trays.

- 1. Remove the screw F attaching the gear cover. Release the two tabs marked **p** by pushing inward.

- 2. Remove the cam gear (2) upward.

- 3. Disconnect the card wire from connector CN083 on the cam switch board assembly.

- 4. Remove the two screws G attaching the cam switch board assembly.

and hole as shown in Fig.17.

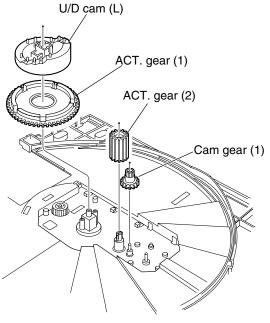

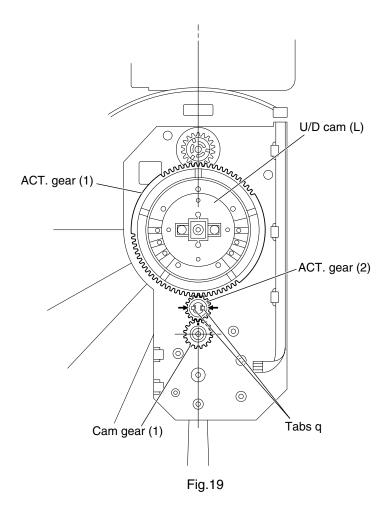

### Removing the ACT. gear (1), U/D cam (L), cam gear (1) and ACT.gear (2) (See Fig.18 and 19)

- Prior to performing the following procedure, remove the main tray cover, the U/D cam (U) and the sub trays.

- 1. Draw out the U/D cam (L).

- 2. Draw out the ACT. gear (1).

- 3. Draw out the cam gear (1).

- 4. Draw out the ACT. gear (2) while pushing the two

CAUTION: When reassembling, make sure the position of each gear referring to Fig.19 and reattach the ACT. gear (2) first.

Fig.18

# Adjustment method

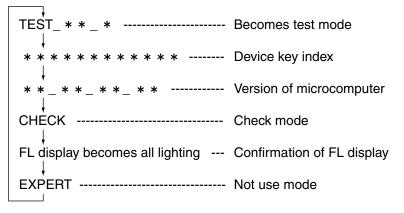

# (1) Test mode setting method

1)Take out the disc and close the tray.

2)Unplug the power plug.

3)Insert power plug into outlet while pressing both "PLAY" button and "STOP" button of the main body.

4)The player displays "TEST \*\* \* " on the FL display. keeps pushing the button until this is displayed.

" \* \* \* " means the player version.

5)When the power supply is turned off, test mode is released.

The mode changes as follows whenever the "CHOICE" button of remote controller is pushed in test mode.

# (2) Initialization method

Please initialize according to the following procedures when microprocessor or pick-up is exchanged and when the up-grade is done.

1)Makes to test mode.

2)After "FORWARD SKIP" button ( ►►) of the main body is pushed, "PAUSE" button is pushed.

3)DVD AUDIO indicator lights when about ten seconds pass. Then, it is initialization completion.

# (3) Method of displaying device key index

1)Makes to test mode and initializes.

2)When "CHOICE" button of remote controller is pushed once, the device key index is displayed on the FL display as follows.

\*\*\*\*\*\*\*

FL Display

\* is a figure or an alphabet.

# (4) Method of displaying version of microcomputer

1)Makes to test mode and initializes

2)When "CHOICE" button of remote controller is pushed twice, the figure is displayed on the FL display as follows.

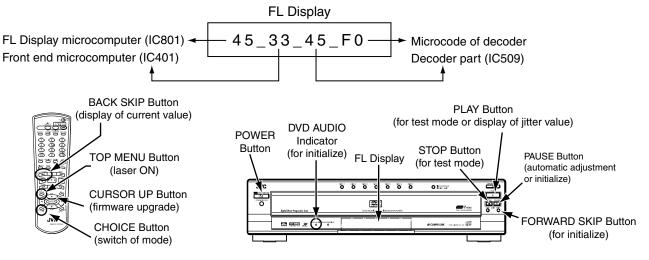

### (5) Display of current value of laser

1)Makes to test mode and initializes

- 2)When "CHOICE" button of remote controller is pushed three times, It is displayed on the FL display, "CHECK".

- 3) The display of FL display changes from "CHECK" into "LD\_ON" if the "TOP MENU" button of remote controller is pushed.

- 4)The laser is turned on if the "BACK SKIP" button ( ► ) of remote controller is pushed in the state, and the current value of the laser is displayed on the FL display.

As for the current value of the laser, the figure displayed on the FL display becomes a current value as it is by "mA" unit. becomes 42mA if displayed as 42.

5)The laser changes from DVD into CD if 3) and 4) of the above-mentioned procedures are done after the trav is opened and closed pushing the "OPEN/CLOSE" button of the main body.

(The laser changes whenever this is done. Moreover, the value displayed first is a laser electric current of DVD.)

# If the laser current value is 64mA or less, it is roughly good. There is a possibility to which pick-up is deteriorated, and exchange pick-up, please when there are 65mA or more laser current value.

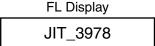

# (6) Display of jitter value

1)Makes to test mode and initializes

- 2)When "CHOICE" button of remote controller is pushed three times, It is displayed on the FL display, "CHECK". 3)The automatic adjustment starts when test disk (VT-501) is inserted, and "PAUSE" button of the main body

- is pushed.

4)When the display of the FL display changes into "CHECK OK", the "PLAY" button of the main body is pushed. 5)The jitter value is displayed on the FL display as follows.

The jitter value is displayed by the hexadecimal number and refer to the conversion table of following, please.

If the indication value is 11% or less, it can be judged by this simple checking method that the signal read precision of the set is satisfactory.

Please do "Flap adjustment of the pick-up guide shaft" when you replace the pick-up and the spindle motor when there are 11% or more jitter value.

|            | value               |            |                        |            |                     |            |                        |

|------------|---------------------|------------|------------------------|------------|---------------------|------------|------------------------|

| FL display | Conversion value(%) | FL display | Conversion<br>value(%) | FL display | Conversion value(%) | FL display | Conversion<br>value(%) |

| 3818       | 4.7                 | 3998       | 7.6                    | 3B18       | 10.5                | 3C98       | 13.3                   |

| 3828       | 4.8                 | 39A8       | 7.7                    | 3B28       | 10.6                | 3CA8       | 13.5                   |

| 3838       | 4.9                 | 39B8       | 7.8                    | 3B38       | 10.7                | 3CB8       | 13.6                   |

| 3848       | 5.1                 | 39C8       | 7.9                    | 3B48       | 10.8                | 3CC8       | 13.7                   |

| 3858       | 5.2                 | 39D8       | 8.1                    | 3B58       | 10.9                | 3CD8       | 13.8                   |

| 3868       | 5.3                 | 39E8       | 8.2                    | 3B68       | 11.1                | 3CE8       | 13.9                   |

| 3878       | 5.4                 | 39F8       | 8.3                    | 3B78       | 11.2                | 3CF8       | 14.1                   |

| 3888       | 5.5                 | 3A18       | 8.5                    | 3B88       | 11.3                | 3D18       | 14.3                   |

| 3898       | 5.7                 | 3A28       | 8.7                    | 3B98       | 11.4                | 3D28       | 14.4                   |

| 38A8       | 5.8                 | 3A38       | 8.8                    | 3BA8       | 11.5                | 3D38       | 14.5                   |

| 38b8       | 5.9                 | 3A48       | 8.9                    | 3BB8       | 11.7                | 3D48       | 14.7                   |

| 38c8       | 6.0                 | 3A58       | 9.0                    | 3BC8       | 11.8                | 3D58       | 14.8                   |

| 38d8       | 6.1                 | 3A68       | 9.1                    | 3BD8       | 11.9                | 3D68       | 14.9                   |

| 38E8       | 6.3                 | 3A78       | 9.3                    | 3BE8       | 12.0                | 3D78       | 15.0                   |

| 38F8       | 6.4                 | 3A88       | 9.4                    | 3BF8       | 12.1                | 3D88       | 15.1                   |

| 3918       | 6.6                 | 3A98       | 9.5                    | 3C18       | 12.4                | 3D98       | 15.3                   |

| 3928       | 6.7                 | 3AA8       | 9.6                    | 3C28       | 12.5                | 3DA8       | 15.4                   |

| 3938       | 6.9                 | 3AB8       | 9.7                    | 3C38       | 12.7                | 3DB8       | 15.5                   |

| 3948       | 7.0                 | 3AC8       | 9.9                    | 3C48       | 12.7                | 3DC8       | 15.6                   |

| 3958       | 7.1                 | 3AD8       | 10.0                   | 3C58       | 12.9                | 3DD8       | 15.7                   |

| 3968       | 7.2                 | 3AE8       | 10.1                   | 3C68       | 13.0                | 3DE8       | 15.9                   |

| 3978       | 7.3                 | 3AF8       | 10.2                   | 3C78       | 13.1                | 3DF8       | 16.0                   |

| 3988       | 7.5                 |            |                        | 3C88       | 13.2                |            |                        |

|            |                     |            |                        |            |                     |            |                        |

#### Jitter value

### XV-FA90BK/XV-FA92SL/XV-FA95GD

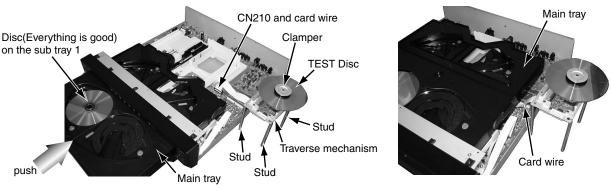

# (7) Flap adjustment of the pick-up guide shaft

| <tool adjustment="" for="" list=""></tool> |      |

|--------------------------------------------|------|

| Stud (four pieces set)                     | Å    |

| Parts No. : JIGXVS40                       |      |

| Hex wrench for adjustment                  |      |

| Off-the-shelf (1.3mm)                      |      |

| Test disc                                  |      |

| VT-501 or VT-502                           | Stud |

|                                            |      |

#### <Adjustment preparation>

- 1. The metal cover is detached, the "OPEN/CLOSE" button is pushed, and the tray is done in open.

- 2. The AC plug code is pulled out once in the state.

- 3. Remove the surround audio board and surround audio terminal board respectively.

- 4. The traverse mechanism is detached, and the card wire is connected with CN210.

- 5. The stud is installed in the traverse mechanism as shown in Figure.

- The clamper is removed from the clamper base.

- 6. The disk (Everything is good) is put on sub-tray 1, the test disk is put on the turntable in the traverse mechanism, and fixes by the clamper.

- 7. The card wire becomes under the main tray, and the main tray is closed by hand operated.

- The AC plug code is inserted, and the "DISC1" button is pushed (Please push the "DISC1" button directly without pushing the power supply button).

- 9. Because the playback of "DISC1" starts, stops and the AC plug code is pulled out.

<Adjustment method>

- 10. The AC plug code is made insertion test mode while pushing the "PLAY" button and the "STOP" button of the main body at the same time.

- 11.Please push the "PAUSE" button after pushing the "FORWARD SKIP" button of the main body, and confirm DVD AUDIO indicator lights after a few seconds.

- 12.When the "CHOICE" button of remote controller is pushed three times, it is displayed on the FL display as "CHECK".

- 13. The display of the FL display changes into "CHECK OK" after a few seconds if the "PAUSE" button of the main body is pushed in the state.

When the "PLAY" button of the main body is pushed afterwards, the jitter value is displayed on the FL display.

#### <Adjustment>

- 1.Puts into the state to display the jitter value on the FL display referring to "(6) Display of jitter value".

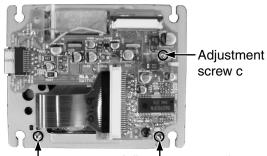

- 2. The adjustment screw under the traverse mechanism is turned with hex wrench, and matches so that the jitter value displayed on the FL display may become minimum value.

#### Adjustment screw a

Adjustment screw b

# <POINT>

- 1.turns in the forward or the opposite direction, and makes to the position where the jitter value is good the half rotation of adjustment screw a and b(180 degrees) respectively.

- 2.Afterwards, adjustment screw b and c are turned in the same way, and makes to the best position.

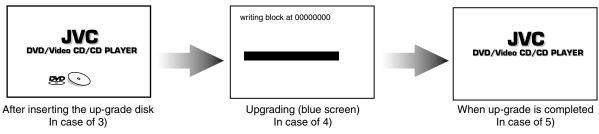

### (8) Upgrading of firmware

#### Please do the up-grade of the firmware after exchanging IC509,IC512,IC513.

1)The power supply is turned on pushing the "POWER" button.

- 2)The up-grade disk is put on sub-tray 1 pushing OPEN/CLOSE button, and the DISC1 button of the main body is pushed.

- 3)When FL display of the main body changes from "READING" into "UPGRADE", cursor UP button ( ) of remote controller is pushed.

- 4)The up-grade starts if the entire screen becomes blue and it is displayed, "writing block at 00000000".

5)The up-grade disk is taken out pushing the OPEN/CLOSE button when returning to the normal screen.

6)Please confirm the version of the microcomputer after makes to test mode and initializes.

<Display of TV screen>

## < ATTENTION ! >

Please pull out the AC plug code after the standby indicator lights pushing the power supply button without fail after completing the repair.

The mechanism becomes initialed position.

There is a possibility to break when carrying in not initialed position the mechanism but the state.

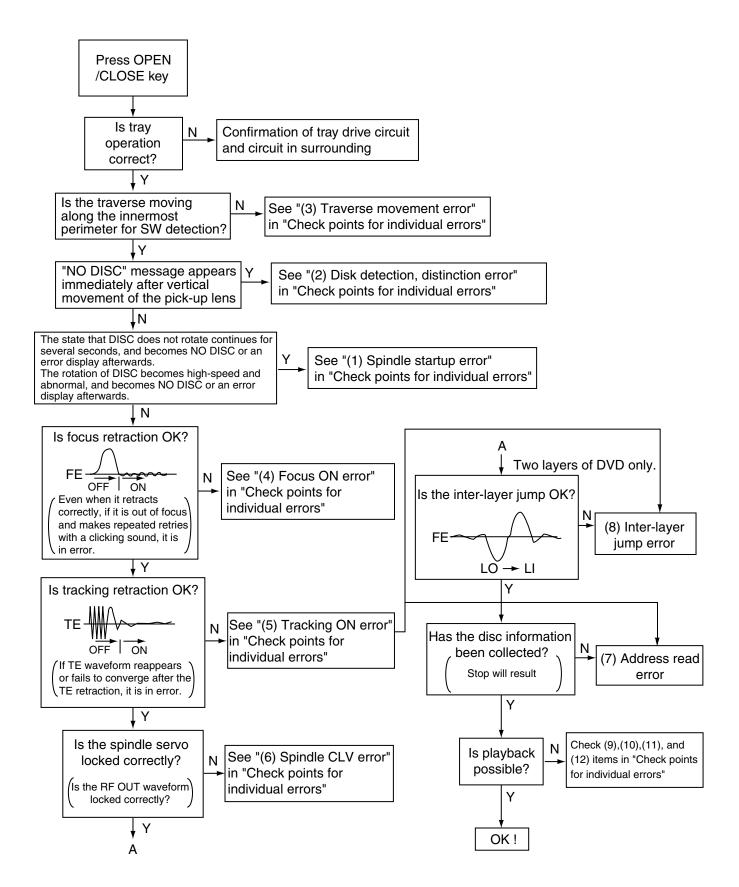

# Troubleshooting

Servo volume

#### XV-FA90BK/XV-FA92SL/XV-FA95GD

# Check points for each error

- (1) Spindle start error

- 1.Defective spindle motor

\*Are there several ohms resistance between each pin of CN201 "11-10","10-9","11-9"? (The power supply is turned off and measured.)

\*Is the sign wave of about 100mVp-p in the voltage had from each terminal? [CN201"6"(H1-),"7"(H1+),"4"(H2-),"5"(H2+),"2"(H3-),"3"(H3+)]

2.Defective spindle motor driver (IC251)

- \*Has motor drive voltage of a sine wave or a rectangular wave gone out to each terminal(SM1~3) of CN201"9,10,11" and IC251"2,4,7"?

- \*Is FG pulse output from the terminal of IC251"24"(FG) according to the rotation of the motor?

\*Is it "L(about 0.9V)" while terminal of IC251"15"(VH) is rotating the motor?

3.Has the control signal come from servo IC or the microcomputer?

\*Is it "L" while the terminal of IC251"18"(SBRK) is operating? Is it "H" while the terminal of IC251"23"(/SPMUTE) is operating?

\*Is the control signal input to the terminal of IC251"22"(EC)? (changes from VHALF voltage while the motor is working.)

\*Is the VHALF voltage input to the terminal of IC251"21"(ECR)?

4.Is the FG signal input to the servo IC?

\*Is FG pulse input to the terminal of IC201"53"(FG) according to the rotation of the motor?

(2) Disc Detection, Distinction error (no disc, no RFENV)

#### <About frontend section>

- \* Laser is defective.

- \* Front End Processor is defective (IC101).

- \* APC circuit is defective. --- Q101,Q102.

- \* Pattern is defective. --- Lines for CN101 All patterns which relate to pick-up and patterns between IC101

- \* Servo IC is defective (IC201).

- \* IC101 --- For signal from IC101 to IC201, is signal output from IC101 "20" (ASOUT) and IC101 "41"(RFENV) and IC101 "22" (FEOUT)?

<About loading mechanism section>

\* The disc exists in a sub tray. However, a sub tray is sent as follows the turntable without rising. (Especially, when the disk is CD-RW)

--- IC81 is defective. Exchanges for "GP2S28J" of the rank specification parts.

### XV-FA90BK/XV-FA92SL/XV-FA95GD

- (3) Traverse movement NG

- 1.Defective traverse driver \*Has the voltage come between terminal of CN101 "15" and "13" ?

- 2.Defective BTL driver (IC271) \*Has the motor drive voltage gone out to IC271"17" or "18"?

- 3.Has the control signal come from servo IC or the microcomputer? \*Is it "H" while the terminal of IC271"9"(STBY1) ? \*TRSDRV Is the signal input? (IC201 "51")

- 4.TRVSW is the signal input from microcomputer? (IC401 "50")

#### (4) Focus ON NG

- \* Is FE output ? --- Pattern, IC101

- \* Is FODRV signal sent ? (R279) --- Pattern, IC201

- \* Is driving voltage sent ?

- IC271 "13", "14" --- If NG, pattern, driver, mechanical unit .

- \* Mechanical unit is defective.

#### (5) Tracking ON NG

- \* When the tracking loop cannot be drawn in, TE shape of waves does not settle.

- \* Mechanical unit is defective.

- Because the self adjustment cannot be normally adjusted, the thing which cannot be normally drawn in is thought.

- \* Periphery of driver (IC271)

- Constant or IC it self is defective.

- \* Servo IC (IC201)

- When improperly adjusted due to defective IC.

- (6) Spindle CLV NG

- \* IC101 -- "35"(RF OUT), "30"(RF-), "31(RF+).

- \* Does not the input or the output of driver's spindle signal do the grip?

- \* Has the tracking been turned on?

- \* Spindle motor and driver is defective.

- \* Additionally, "IC101 and IC201" and "Mechanism is defective(jitter)", etc. are thought.

- (7) Address read NG

- \* Besides, the undermentioned cause is thought though specific of the cause is difficult because various factors are thought.

Mechanism is defective. (jitter) IC201, IC301, IC401. The disc is dirty or the wound has adhered.

(8) Between layers jump NG (double-layer disc only)

Mechanism defective Defect of driver's IC(IC271) Defect of servo control IC(IC201)

- (9) Neither picture nor sound is output

- 1.It is not possible to search

\*Has the tracking been turned on?

\*To "(5) Tracking ON NG" in "Check points for each error" when the tracking is not normal.

\*Is the feed operation normal?

To "(3) traverse movement NG" in "Check points for each error" when it is not normal.

Are not there caught of the feeding mechanism etc?

(10) Picture is distorted or abnormal sound occurs at intervals of several seconds.

Is the feed operation normal?

Are not there caught of the feeding mechanism etc?

(11) Others

The image is sometimes blocked, and the image stops. The image is blocked when going to outer though it is normal in surroundings in the disk and the stopping symptom increases.

NO

There is a possibility with bad jitter value for such a symptom.

(12) CD During normal playback operation

a) Is TOC reading normal? Displays total time for CD-DA. Shifts to double-speed mode for V-CD.

b)Playback possible?

\*--:-- is displayed during FL search. According to [It is not possible to search ] for DVD(9), check the feed and tracking systems.

\*No sound is output although the time is displayed.(CA-DA) DAC, etc, other than servo.

\*The passage of time is not stable, or picture is abnormal.(V-CD)

\*The wound of the disc and dirt are confirmed.

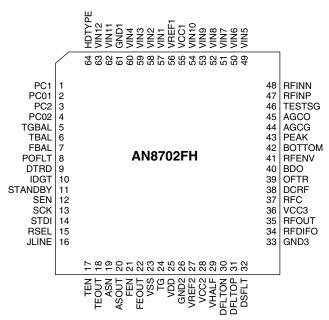

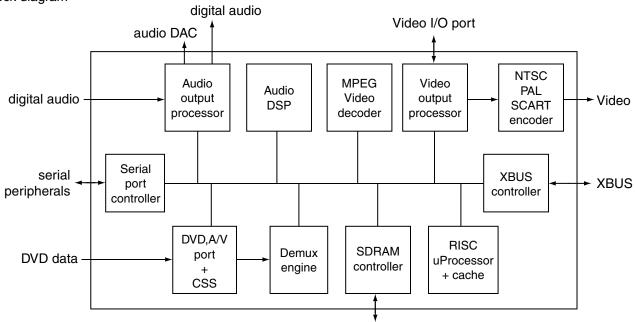

# **Description of major ICs**

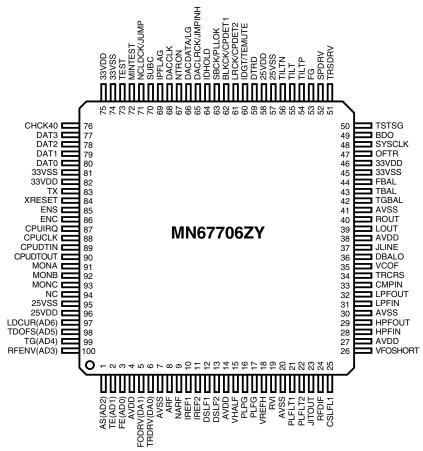

# AN8702FH(IC101):Frontend processor

1.Pin layout

#### 2.Pin function

| Pin No. | Symbol      | I/O | Description                                           | Pin No. | Symbol | I/O    | Description                                        |

|---------|-------------|-----|-------------------------------------------------------|---------|--------|--------|----------------------------------------------------|

|         | PC1         | 1/0 | Disc detection signal input (DVD)                     | 34      | RFDIFO | 1/0    | Description                                        |

| 1 2     | PC1<br>PC01 | 1/0 | Laser current control terminal                        | 35      | RFOUT  | -      | To TP101                                           |

| 2       | PC01<br>PC2 | 1/0 | Disc detection signal input (CD)                      | 36      | VCC3   | -      | Power supply terminal 5V                           |

| 4       | PC02        | 1/O | Laser current control terminal                        | 37      | RFC    | -      |                                                    |

| 5       | TGBAL       | 10  | Tangential phase balance control terminal             | 38      | DCRF   | 0      | All addition amplifier capacitor terminal          |

| 6       | TBAL        | 1   | Tracking balance control terminal                     | 39      | OFTR   | 0      | OFTR output terminal                               |

| 7       | FBAL        | 1   | Focus balance control terminal                        | 40      | BDO    | 0      | Drop out                                           |

| 8       | POFLT       | 0   | Track detection threshold level terminal              | 41      | RFENV  | 0      | RF envelope output terminal                        |

| 9       | DTRD        | 1   | Data slice part data read signal input terminal       | 42      | BOTTOM | 0      | Bottom envelope detection filter terminal          |

| 3       | DIND        | •   | (For RAM)                                             | 43      | PEAK   | 0      | Peak envelope detection filter terminal            |

| 10      | IDGT        | I   | Data slice part address part gate signal input        | 44      | AGCG   | 0      | AGC amplifier gain control terminal                |

| 10      | ibai        | •   | terminal( For RAM)                                    | 45      | AGCO   |        |                                                    |

| 11      | STANDBY     | I   | Standby mode control terminal                         | 46      | TESTSG | 1      | TEST signal input terminal                         |

| 12      | SEN         |     | SEN(Serial data input terminal)                       | 47      | RFINP  | i      | RF signal positive input terminal                  |

| 13      | SCK         |     | SCK(Serial data input terminal)                       | 48      | RFINN  | · ·    | RF signal negative input terminal                  |

| 14      | STDI        |     | STDI(Serial data input terminal)                      | 49      | VIN5   | i i    | Focus input of external division into two terminal |

| 15      | RSEL        |     |                                                       | 50      | VIN6   | ·<br>· | Focus input of external division into two terminal |

| 16      | JLINE       | 1   | J-line setting input(FEP)                             | 51      | VIN7   | 1      |                                                    |

| 17      | TEN         | -   |                                                       | 52      | VIN8   | 1      |                                                    |

| 18      | TEOUT       | 0   | Tracking error signal output terminal                 | 53      | VIN9   | 1      | Focus input of external division into two terminal |

| 19      | ASN         |     | ······································                | 54      | VIN10  | 1      | Focus input of external division into two terminal |

| 20      | ASOUT       | 0   | Full adder signal output                              | 55      | VCC1   | -      | Power supply terminal 5V                           |

| 21      | FEN         | Ι   | Focus error output amplifier reversing input terminal | 56      | VREF1  | 0      | VREF1 voltage output terminal                      |

| 22      | FEOUT       | 0   | Focus error signal output terminal                    | 57      | VIN1   | 1      | External division into four (DVD/CD) RF input      |

| 23      | VSS         | -   | Connect to GND                                        |         |        |        | terminal1                                          |

| 24      | TG          | 0   | Tangential phase error signal output terminal         | 58      | VIN2   | Ι      | External division into four (DVD/CD) RF input      |

| 25      | VDD         | -   | Power supply terminal 3V                              |         |        |        | terminal2                                          |

| 26      | GND2        | -   | Connect to GND                                        | 59      | VIN3   | Ι      | External division into four (DVD/CD) RF input      |

| 27      | VREF2       | 0   | VREF2 voltage output terminal                         |         |        |        | terminal3                                          |

| 28      | VCC2        | -   | Power supply terminal 5V                              | 60      | VIN4   | Ι      | External division into four (DVD/CD) RF input      |

| 29      | VHALF       | 0   | VHALF voltage output terminal                         | 1       |        |        | terminal4                                          |

| 30      | DFLTON      | 0   | Equivalence RF-                                       | 61      | GND1   | -      | Connect to GND                                     |

| 31      | DFLTOP      | 0   | Equivalence RF+                                       | 62      | VIN11  | Ι      | Tracking input                                     |

| 32      | DSFLT       |     |                                                       | 63      | VIN12  | Ι      | Tracking input                                     |

| 33      | GND3        | -   | Connect to GND                                        | 64      | HDTYPE | -      | Connect to ground                                  |

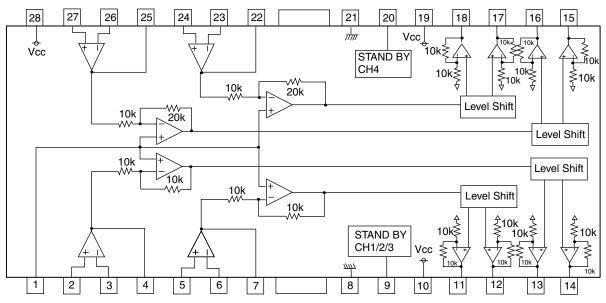

## ■ BA5983FM-X (IC271) : 4CH DRIVER

#### 1.Block diagram

#### 2.Pin function

| Pin No. | Symbol   | I/O | Function                           | Pin No. | Symbol   | I/O | Function                           |

|---------|----------|-----|------------------------------------|---------|----------|-----|------------------------------------|

| 1       | BIAS IN  | I   | Input for Bias-amplifier           | 15      | VO4(+)   | 0   | Non inverted output of CH4         |

| 2       | OPIN1(+) | Ι   | Non inverting input for CH1 OP-AMP | 16      | VO4(-)   | 0   | Inverted output of CH4             |

| 3       | OPIN1(-) | Ι   | Inverting input for CH1 OP-AMP     | 17      | VO3(+)   | 0   | Non inverted output of CH3         |

| 4       | OPOUT1   | 0   | Output for CH1 OP-AMP              | 18      | VO3(-)   | 0   | Inverted output of CH3             |

| 5       | OPIN2(+) | Ι   | Non inverting input for CH2 OP-AMP | 19      | PowVcc2  | -   | Vcc for CH3/4 power block          |

| 6       | OPIN2(-) | Ι   | Inverting input for CH2 OP-AMP     | 20      | STBY2    | I   | Input for Ch4 stand by control     |

| 7       | OPOUT2   | 0   | Output for CH2 OP-AMP              | 21      | GND      | -   | Substrate ground                   |

| 8       | GND      | -   | Substrate ground                   | 22      | OPOUT3   | 0   | Output for CH3 OP-AMP              |

| 9       | STBY1    | Ι   | Input for CH1/2/3 stand by control | 23      | OPIN3(-) | Ι   | Inverting input for CH3 OP-AMP     |

| 10      | PowVcc1  | -   | Vcc for CH1/2 power block          | 24      | OPIN3(+) | Ι   | Non inverting input for CH3 OP-AMP |

| 11      | VO2(-)   | 0   | Inverted output of CH2             | 25      | OPOUT4   | 0   | Output for CH4 OP-AMP              |

| 12      | VO2(+)   | 0   | Non inverted output of CH2         | 26      | OPIN4(-) | I   | Inverting input for CH4 OP-AMP     |

| 13      | VO1(-)   | 0   | Inverted output of CH1             | 27      | OPIN4(+) | I   | Non inverting input for CH4 OP-AMP |

| 14      | VO1(+)   | 0   | Non inverted output of CH1         | 28      | PreVcc   | -   | Vcc for pre block                  |

### ■ 74LCX373MTC-X(IC512,IC513)

#### 1.Pin layout

#### 2.Pin function

| OE  | 1  | $\smile$ 20 | VCC |

|-----|----|-------------|-----|

| Q0  | 2  | 19          | Q7  |

| D0  | 3  | 18          | D7  |

| D1  | 4  | 17          | D6  |

| Q1  | 5  | 16          | Q6  |

| Q2  | 6  | 15          | Q5  |

| D2  | 7  | 14          | D5  |

| D3  | 8  | 13          | D4  |

| Q3  | 9  | 12          | Q4  |

| GND | 10 | 11          | LE  |

| Symbol | Description           |

|--------|-----------------------|

| D0~D7  | Data inputs           |

| LE     | Latch enable input    |

| ŌĒ     | Output enable input   |

| Q0~Q7  | 3-State latch outputs |

|        |                       |

#### 3.Truth table

|    | INPUTS |    | OUTPUTS |

|----|--------|----|---------|

| LE | OE     | Dn | Qn      |

| X  | Н      | Х  | Z       |

| н  | L      | L  | L       |

| н  | L      | н  | Н       |

| L  | L      | x  | Q0      |

H = HIGH Voltage level

L = LOW Voltage level

Z = High impedanceX = Immaterial

Q0 = Previous Q0 before HIGH to LOW transition of latch enable

# ■ BA6664FM-X(IC251):Spindle motor driver

1.Pin layout

| NC  | 1  | $\bigcirc_{28}$ | RNF |  |

|-----|----|-----------------|-----|--|

|     |    |                 |     |  |

| A3  | 2  | 27              | VM  |  |

| NC  | 3  | 26              | GSW |  |

| A2  | 4  | 25              | VCC |  |

| NC  | 5  | 24              | FG  |  |

| NC  | 6  | 23              | PS  |  |

| A1  | 7  | 22              | EC  |  |

|     | 29 | 30              |     |  |

| GND | 8  | 21              | ECR |  |

| H1+ | 9  | 20              | FR  |  |

| H1- | 10 | 19              | FG2 |  |

| H2+ | 11 | 18              | SB  |  |

| H2- | 12 | 17              | CNF |  |

| H3+ | 13 | 16              | BR  |  |

| H3- | 14 | 15              | VH  |  |

|     |    |                 |     |  |

#### 2.Pin function

| Pin No. | Symbol | I/O | Description                                        |  |  |  |

|---------|--------|-----|----------------------------------------------------|--|--|--|

| 1       | NC     | -   | Non connect                                        |  |  |  |

| 2       | A3     | 0   | Output 3 for spindle motor                         |  |  |  |

| 3       | NC     | -   | Non connect                                        |  |  |  |

| 4       | A2     | 0   | Output 2 for spindle motor                         |  |  |  |

| 5       | NC     | -   | Non connect                                        |  |  |  |

| 6       | NC     | -   | Non connect                                        |  |  |  |

| 7       | A1     | 0   | Output 1 for spindle motor                         |  |  |  |

| 8       | GND    | -   | Connect to ground                                  |  |  |  |

| 9       | H1+    | Ι   | Positive input for hall input AMP 1                |  |  |  |

| 10      | H1-    |     | Negative input for hall input AMP 2                |  |  |  |

| 11      | H2+    | I   | Positive input for hall input AMP 2                |  |  |  |

| 12      | H2-    |     | Negative input for hall input AMP 2                |  |  |  |

| 13      | H3+    | Ι   | Positive input for hall input AMP 3                |  |  |  |

| 14      | H3-    |     | Negative input for hall input AMP 3                |  |  |  |

| 15      | VH     |     | Hall bias terminal                                 |  |  |  |

| 16      | BR     | -   | Non connect                                        |  |  |  |

| 17      | CNF    | -   | Capacitor connection pin for phase compensation    |  |  |  |

| 18      | SB     | 0   | Short brake terminal                               |  |  |  |

| 19      | FG2    | -   | Non connect                                        |  |  |  |

| 20      | FR     | -   | Non connect                                        |  |  |  |

| 21      | ECR    |     | Torque control standard voltage input terminal     |  |  |  |

| 22      | EC     | I   | Torque control voltage input terminal              |  |  |  |

| 23      | PS     | 0   | Start/stop switch (power save terminal)            |  |  |  |

| 24      | FG     | 0   | FG signal output terminal                          |  |  |  |

| 25      | VCC    | -   | Power supply for signal division                   |  |  |  |

| 26      | GSW    | 0   | Gain switch                                        |  |  |  |

| 27      | VM     | -   | Power supply for driver division                   |  |  |  |

| 28      | RNF    | 0   | Resistance connection pin for output current sense |  |  |  |

| 29      |        | -   | Connect to ground                                  |  |  |  |

| 30      |        | -   | Connect to ground                                  |  |  |  |

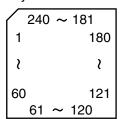

# ■ JCV8005-3(IC500):CPPM (Content protection for pre-recorded media)

1.Pin layout

|     | 80 | )~ | 51 |    |

|-----|----|----|----|----|

| 81  |    |    |    | 50 |

| 2   |    |    |    | ٢  |

| 100 |    |    |    | 31 |

|     | 1  | ~  | 30 |    |

2.Pin function

JCV8005-3 1/2

| Pin No. | Symbol     | I/O | Description                                             |

|---------|------------|-----|---------------------------------------------------------|

| 1       | VDD        | -   | Power supply                                            |

| 2       | GND        | -   | Connect to ground                                       |

| 3~10    | HDATA0~7   | I/O | Data input/output terminal (both by 8 bits)             |

| 11      | VDD        | -   | Power supply                                            |

| 12      | GND        | -   | Connect to ground                                       |

| 13~20   | HADDR0~7   | I   | 8 bit address bus to internal address (connect to host) |

| 21      | VDD        | -   | Power supply                                            |

| 22      | GND        | -   | Connect to ground                                       |

| 23      | NCS        | I   | Chip select signal from host                            |

| 24      | NRD        | I   | Data read signal from host                              |

| 25      | NWR        | I   | Data write signal from host                             |

| 26      | NIRQ       | 0   | Interrupt of request to host                            |

| 27      | WAIT       | 0   | Wait demand to host                                     |

| 28      | NRESET     | I   | Reset signal from host                                  |

| 29      | VDD        | -   | Power supply                                            |

| 30      | GND        | -   | Connect to ground                                       |

| 31      | VDD        | -   | Power supply                                            |

| 32      | GND        | -   | Connect to ground                                       |

| 33~36   | STD7~4_OUT | 0   | Data output to DVD decoder (8 bits)                     |

| 37      | GND        | -   | Connect to ground                                       |

| 38~41   | STD3~0_OUT | 0   | Data output to DVD decoder (8 bits)                     |

| 42      | VDD        | -   | Power supply                                            |

| 43      | GND        | -   | Connect to ground                                       |

| 44      | REQ_IN     | I   | Request signal for forwarding control by decoder        |

| 45      | DACK_OUT   | 0   | Output signal to decoder which shows effective data     |

| 46      | STCLK_OUT  | 0   | Data strobe signal to decoder                           |

| 47      | SYNC_OUT   | 0   | Sector sink signal to decoder                           |

| 48      | STERROUT   | -   | Non connect                                             |

| 49      | VDD        | -   | Power supply                                            |

| 50      | GND        | -   | Connect to ground                                       |

| 51      | VDD        | -   | Power supply                                            |

| 52      | GND        | -   | Connect to ground                                       |

| 53      | G_NRD      | I   | Glue logic input signal from host                       |

| 54      | G_NWR      | I   | Glue logic input signal from host                       |

| 55      | G_WITODC   | I   | Glue logic input signal from front end                  |

| 56      | G_CSDEC    | I   | Glue logic input signal from host                       |

| 57      | G_WITDEC   | I   | Glue logic input signal from decoder                    |

| 58      | VDD        | -   | Power supply                                            |

2.Pin function

JCV8005-3 2/2

| Pin No.  | Symbol    | I/O | Description                                                  |

|----------|-----------|-----|--------------------------------------------------------------|

|          | GND       | 1/0 | Connect to ground                                            |

| 59<br>60 | WAIT1     | 0   | Glue logic output signal to host                             |

|          |           | 0   | Non connect                                                  |

| 61       | WAIT2     | -   | Glue logic input signal (connect to 27 pin)                  |

| 62       | WAITIN    | I   |                                                              |

| 63       | VDD       | -   | Power supply                                                 |

| 64       | GND       | -   | Connect to ground                                            |

| 65       | TEST_IN   |     | Connect to ground                                            |

| 66,67    | NC        | -   | Non connect                                                  |

| 68       | VDD       | -   | Power supply                                                 |

| 69       | GND       | -   | Connect to ground                                            |

| 70       | CLKOCTL   |     | Input terminal for crystal-oscillator circuit on/off control |

| 71       | NC        | -   | Non connect                                                  |

| 72       | OSCI      | I   | Crystal oscillation terminal (input side)                    |

| 73       | OSCO      | 0   | Crystal oscillation terminal (output side)                   |

| 74       | NC        | -   | Non connect                                                  |

| 75       | VDD       | -   | Power supply                                                 |

| 76       | GND       | -   | Connect to ground                                            |

| 77       | 33OUT     | 0   | Oscillation output terminal                                  |

| 78       | 169OUT    | 0   | Oscillation output terminal                                  |

| 79       | VDD       | -   | Power supply                                                 |

| 80       | GND       | -   | Connect to ground                                            |

| 81       | VDD       | -   | Power supply                                                 |

| 82       | GND       | -   | Connect to ground                                            |

| 83       | STERR_IN  | I   | Presence of data error from front end                        |

| 84       | SYNC_IN   | I   | Sector sink signal from front end                            |

| 85       | STCLK_IN  | I   | Data clock signal from front end                             |

| 86       | DACK_IN   | I   | Signal which shows effective data from front end             |

| 87       | REQ_OUT   | 0   | Request signal for forwarding control to front end           |

| 88       | VDD       | -   | Power supply                                                 |

| 89       | GND       | -   | Connect to ground                                            |

| 90~93    | STD0~3_IN |     | Data input from front end (8 bits)                           |

| 94       | GND       | -   | Connect to ground                                            |

| 95~98    | STD4~7_IN | I   | Data input from front end (8 bits)                           |

| 99       | VDD       | -   | Power supply                                                 |

| 100      | GND       | -   | Connect to ground                                            |

|          | I         |     | -                                                            |

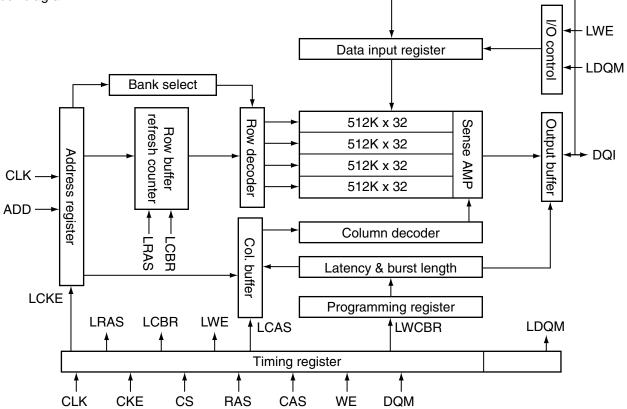

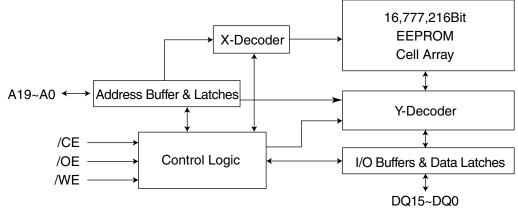

## ■ K4S643232E-TC60(IC505):DRAM

#### 1.Block diagram

2.Pin function

| Symbol | Description               | Symbol | Description            |

|--------|---------------------------|--------|------------------------|

| CLK    | System clock signal input | DQM0~3 | Data input/output mask |

| CS     | Chip select input         | DQ0~31 | Data input/output      |

| CKE    | Clock enable              | VDD    | Power supply terminal  |

| A0~A10 | Address                   | VSS    | Connect to ground      |

| BA0,1  | Bank select address       | VDDQ   | Power supply terminal  |

| RAS    | Row address strobe        | VSSQ   | Connect to ground      |

| CAS    | Column address strobe     | NC     | Non connect            |

| WE     | Write enable              |        |                        |

# ■ MN102L25GGW1(IC401):Unit CPU Pin function

| Pin No. | Symbol  | I/O | Function                       | Pin No. | Symbol  | I/O | Function                       |

|---------|---------|-----|--------------------------------|---------|---------|-----|--------------------------------|

| 1       | WAIT    |     | Micon wait signal input        | 51      | SWUPDN  |     | Elevator UP/DOWN switch detect |

| 2       | RE      | 0   | Read enable                    | 52      | SWOPEN  |     | Tray OPEN/CLOSE switch detect  |

| 3       | SPMUTE  | 0   | Spindle muting output to IC251 | 53      | ADSCEN  | 0   | Serial enable signal for ADSC  |

| 4       | WEN     | 0   | Write enable                   | 54      | VDD     | -   | Power supply                   |

| 5       | LMMUTE  | 0   | Loading motor standby control  | 55      | FEPEN   | 0   | Serial enable signal for FEP   |

| 6       | CS1     | 0   | Chip select for ODC            | 56      | SLEEP   | 0   | Standby signal for FEP         |

| 7       | CS2     | 0   | Chip select for CPPM           | 57      | BUSY    | -   | Non connect                    |

| 8       | CS3     | -   | Connect to TP312               | 58      | REQ     | 0   | Communication Request          |

| 9       | DRVMUTE | 0   | Driver mute                    | 59      | CIRCEN  | 0   | CIRC command select            |

| 10      | SPKICK  | 0   | Spin kick (Non connect)        | 60      | -       | -   | Connect to TP308               |

| 11      | LSIRST  | 0   | LSI reset                      | 61      | VSS     | -   | Ground                         |

| 12      | WORD    | 0   | Bus selection input            | 62      | EPCS    | 0   | EEPROM chip select             |

| 13      | A0      | 0   | Address bus 0 for CPU          | 63      | EPSK    |     | EEPROM clock                   |

| 14      | A1      | 0   | Address bus 1 for CPU          | 64      | DPDI    | Ī   | EEPROM data input              |

| 15      | A2      | 0   | Address bus 2 for CPU          | 65      | EPDO    | 0   | EEPROM data output             |

| 16      | A3      | 0   | Address bus 3 for CPU          | 66      | VDD     | -   | Power supply                   |

| 17      | VDD     | -   | Power supply                   | 67      | SCLKO   | 1   | Communication clock            |

| 18      | SYSCLK  | -   | Connect to TP169               | 68      | S2UDT   |     | Communication input data       |

| 19      | VSS     | -   | Ground                         | 69      | U2SDT   | 0   | Communication output data      |

| 20      | XI      | -   | Not use (Connect to vss)       | 70      | CPSCK   | Ō   | Clock for ADSC serial          |

| 21      | XO      | -   | Connect to TP170               | 71      | SDIN    | Ī   | ADSC serial data input         |

| 22      | VDD     | -   | Power supply                   | 72      | SDOUT   | Ó   | ADSC serial data output        |

| 23      | OSCI    | 1   | Clock signal input             | 73      | -       | -   | Not use                        |

| 24      | OSCO    | Ō   | Clock signal output            | 74      | -       | -   | Not use                        |

| 25      | MODE    |     | CPU Mode selection input       | 75      | NMI     | -   | Not use                        |

| 26      | A4      | 0   | Address bus 4 for CPU          | 76      | ADSCIRQ |     | Interrupt input of ADSC        |

| 27      | A5      | 0   | Address bus 5 for CPU          | 77      | ODCIRQ  | 1   | Interrupt input of ODC         |

| 28      | A6      | 0   | Address bus 6 for CPU          | 78      | DECIRQ  | 1   | Interrupt input of ZIVA        |

| 29      | A7      | 0   | Address bus 7 for CPU          | 79      | CSSIRQ  | -   | Not use                        |

| 30      | A8      | 0   | Address bus 8 for CPU          | 80      | ODCIRQ2 | 1   | Interruption of system control |

| 31      | A9      | 0   | Address bus 9 for CPU          | 81      | ADSEP   | 1   | Address data selection input   |

| 32      | A10     | 0   | Address bus 10 for CPU         | 82      | RST     | 1   | Reset input                    |

| 33      | A11     | 0   | Address bus 11 for CPU         | 83      | VDD     | -   | Power supply                   |

| 34      | VDD     | -   | Power supply                   | 84      | TEST1   | 1   | Test signal 1 input            |

| 35      | A12     | 0   | Address bus 12 for CPU         | 85      | TEST2   | 1   | Test signal 2 input            |

| 36      | A13     |     | Address bus 13 for CPU         | 86      | TEST3   | Ι   | Test signal 3 input            |

| 37      | A14     |     | Address bus 14 for CPU         | 87      | TEST4   | Ι   | Test signal 4 input            |

| 38      | A15     | 0   | Address bus 15 for CPU         | 88      | TEST5   | Ι   | Test signal 5 input            |

| 39      | A16     | 0   | Address bus 16 for CPU         | 89      | TEST6   | Ι   | Test signal 6 input            |

| 40      | A17     | 0   | Address bus 17 for CPU         | 90      | TEST7   | Ι   | Test signal 7 input            |

| 41      | A18     | -   | Connect to TP913               | 91      | TEST8   |     | Test signal 8 input            |

| 42      | A19     | -   | Connect to TP912               | 92      | VSS     | -   | Ground                         |

| 43      | VSS     | -   | Ground                         | 93      | D0      | I/O | Data bus 0 of CPU              |

| 44      | A20     | -   | Connect to TP911               | 94      | D1      | I/O | Data bus 1 of CPU              |

| 45      | TXSEL   | -   | Connect to TP910               | 95      | D2      | I/O | Data bus 2 of CPU              |

| 46      | HAGUP   | 0   |                                | 96      | D3      | I/O | Data bus 3 of CPU              |

| 47      | TCLOSE  | -   | Connect to TP311               | 97      | D4      |     | Data bus 4 of CPU              |

| 48      | TOPEN   | -   | Connect to TP310               | 98      | D5      |     | Data bus 5 of CPU              |

| 49      | HMFON   |     |                                | 99      | D6      |     | Data bus 6 of CPU              |

|         | TRVSW   | I   | Detection switch of traverse   | 100     | D7      |     | Data bus 7 of CPU              |

| 50      |         |     |                                |         |         |     |                                |

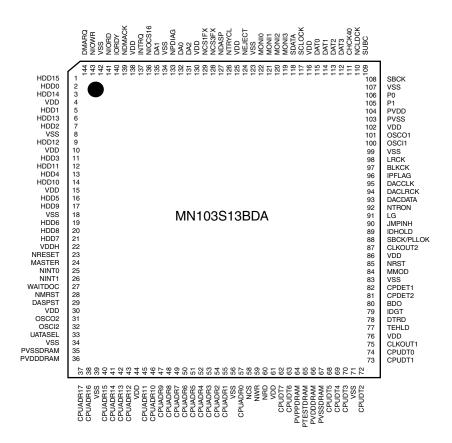

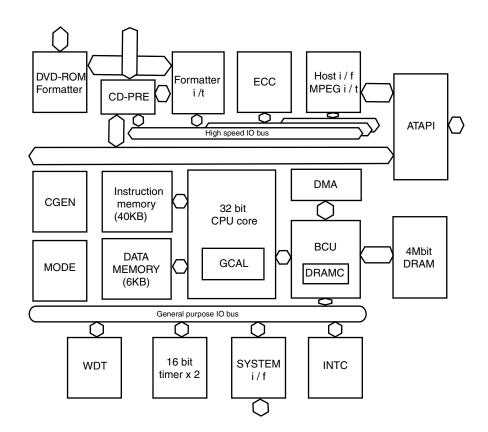

## MN103S13BDA(IC301):Optical disc controller

#### 1.Pin layout

2.Block diagram

### 3.Pin function (1/3)

| Pin No.      | Symbol         | I/O | Description                                |

|--------------|----------------|-----|--------------------------------------------|

| 1            | HDD15          | I/O | ATAPI Data                                 |

| 2            | HDD0           | I/O | ATAPI Data                                 |

| 3            | HDD14          | I/O | ATAPI Data                                 |

| 4            | VDD            | -   | Power supply 3V                            |

| 5            | HDD1           | I/O | ATAPI Data                                 |

| 6            | HDD13          | I/O | ATAPI Data                                 |

| 7            | HDD2           | I/O | ATAPI Data                                 |

| 8            | VSS            | -   | Connect to GND                             |

| 9            | HDD12          | I/O | ATAPI Data                                 |

| 10           | VDD            | -   | Power supply 2.7V                          |

| 11           | HDD3           | I/O | ATAPI Data                                 |

| 12           | HDD11          | I/O | ATAPI Data                                 |

| 13           | HDD4           | I/O | ATAPI Data                                 |

| 14           | HDD10          | I/O | ATAPI Data                                 |

| 15           | VDD            | -   | Power supply 3V                            |

| 16           | HDD5           | I/O | ATAPI Data                                 |

| 17           | HDD9           | I/O | ATAPI Data                                 |

| 18           | VSS            | -   | Connect to GND                             |

| 19           | HDD6           | I/O | ATAPI Data                                 |

| 20           | HDD8           | 1/O | ATAPI Data                                 |

| 21           | HDD7           | 1/O | ATAPI Data                                 |

| 22           | VDDH           | "0  |                                            |

| 23           | NRESET         | 1   | ATAPI Reset input                          |

| 24           | MASTER         | I/O | ATAPI Master/slave select                  |

| 25           | NINT0          | 0   | Interruption of system control 0           |

| 26           | NINT1          | 0   | Interruption of system control 1           |

| 20           | WAITDOC        | 0   | Wait control of system control             |

| 28           | NMRST          | 0   | Reset of system control (Connect to TP302) |

| 20           | DASPST         |     | Setting of initial value of DASP signal    |

| 30           | VDD            | -   | Power supply 3V                            |

| 31           | OSCO2          | 0   | Non connect                                |

| 32           | OSCI2          |     | Non connect                                |

| 33           |                | 1   | Connect to VSS                             |

| 33           | UATASEL<br>VSS | 1   | Connect to GND                             |

| 35           | PVSSDRAM       | -   | Connect to VSS                             |

| 36           | PVDDDRAM       |     | Connect to VDD(2.7V)                       |

| 37           | CPUADR17       | -   | System control address                     |

| 37           |                | 1   | System control address                     |

| 39           | CPUADR16       |     | Connect to GND                             |

| - 39<br>- 40 |                | -   | System control address                     |

| 40           | CPUADR15       |     | System control address                     |

| 41           | CPUADR14       |     | System control address                     |

| 42           | CPUADR13       |     | System control address                     |

| 43           | CPUADR12       |     | Power supply 2.7V                          |

|              |                | -   |                                            |

| 45           | CPUADR11       |     | System control address                     |

| 46           | CPUADR10       |     | System control address                     |

| 47           | CPUADR9        |     | System control address                     |

| 48           | CPUADR8        |     | System control address                     |

| 49           | CPUADR7        |     | System control address                     |